https://developer.arm.com/documentation/101811/latest

What is memory management? 什么是内存管理?

略

Address spaces 地址空间

Armv8-A 中的地址空间:

As well as multiple virtual address spaces, AArch64 also has multiple physical address spaces (PAS):

除了多个虚拟地址空间之外,AArch64 还具有多个物理地址空间(PAS):

Non-secure PAS0

Secure PAS

Realm PAS (Armv9-A only)

Root PAS (Armv9-A only)

Non-secure state: virtual addresses can only map to Non-secure physical addresses.

非安全状态:虚拟地址只能映射到非安全物理地址。

Secure state: virtual addresses can map to Secure or Non-secure physical addresses.

安全状态:虚拟地址可以映射到安全或非安全物理地址。

Realm state: virtual addresses can map to Realm or Non-secure physical addresses

Realm状态:虚拟地址可以映射到Realm或非安全物理地址

Root state: virtual address can map to any physical address space.

根状态:虚拟地址可以映射到任意物理地址空间。

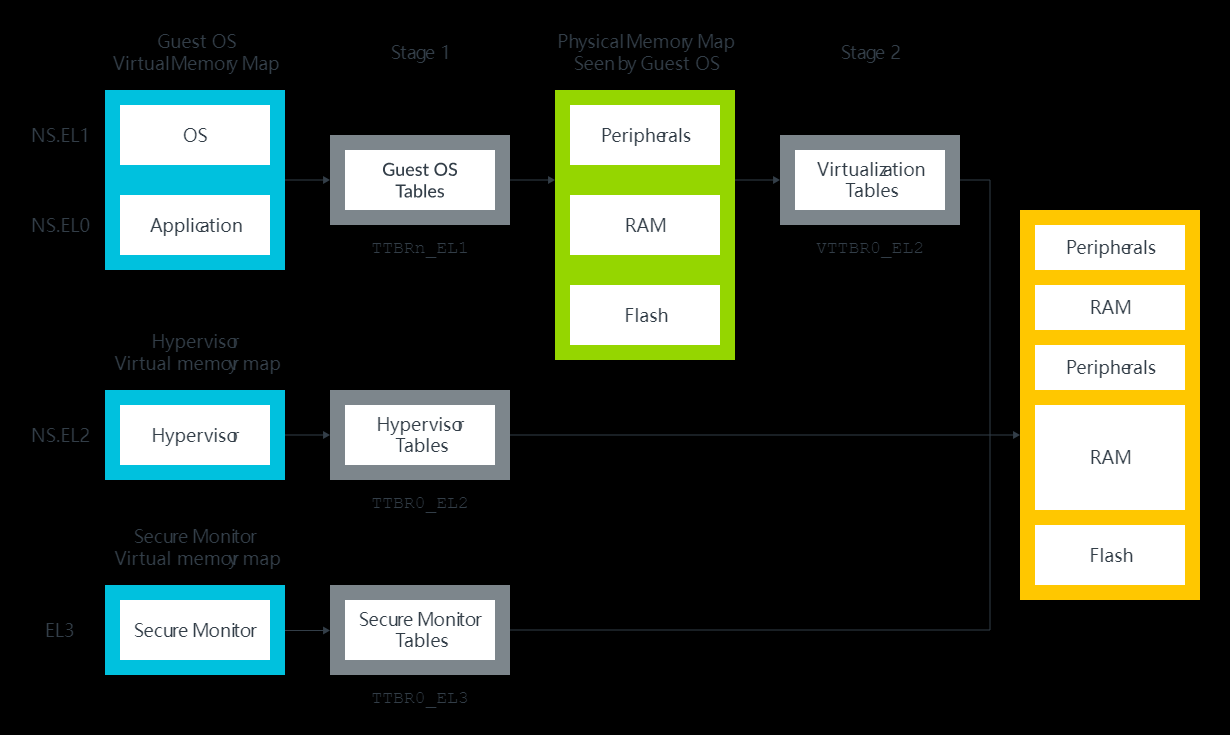

intermediate physical addresses(IPA)中间物理地址

多个物理地址空间的映射:

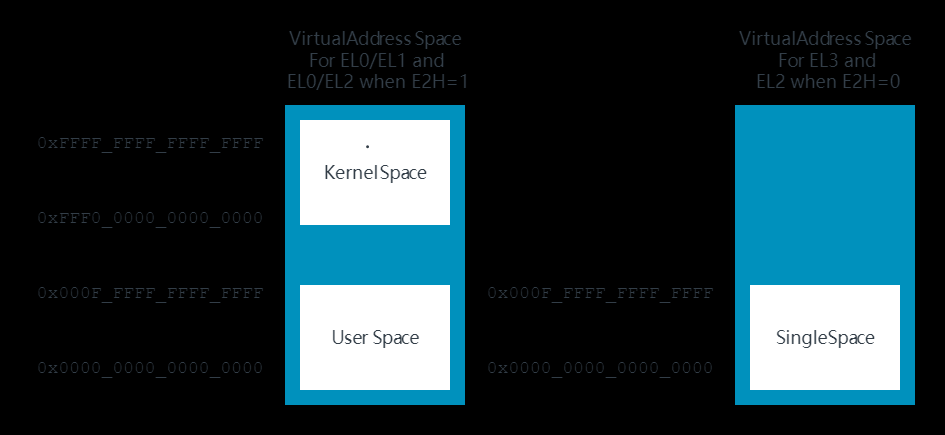

HCR_EL2.E2H

在 ARM 架构中,E2H 是 SCR_EL3(Secure Configuration Register at EL3)寄存器中的一个控制位,主要用于配置 EL2(Hypervisor Exception Level)的行为方式。具体来说,E2H 位决定了 EL2 是以 "Hyp" 模式还是以 "Host" 模式运行。

E2H 位的含义:

E2H = 0: EL2 处于 "Hyp" 模式,兼容传统的虚拟化行为。

在这种模式下,EL2 的行为更像是经典的虚拟化层,允许在 EL2 中运行虚拟机管理程序(Hypervisor)并支持虚拟化功能。

在这种模式下,EL2 拥有完整的虚拟化支持能力。

E2H = 1: EL2 处于 "Host" 模式,更加接近 EL1 的行为。

在这个模式下,EL2 更像是一个普通的执行级别,且通常与虚拟化操作有所不同。主要用于新的系统架构设计,比如在一些高级虚拟化场景下需要调整 EL2 的行为方式。

这种模式下,EL2 的一些虚拟化功能可能会被限制。

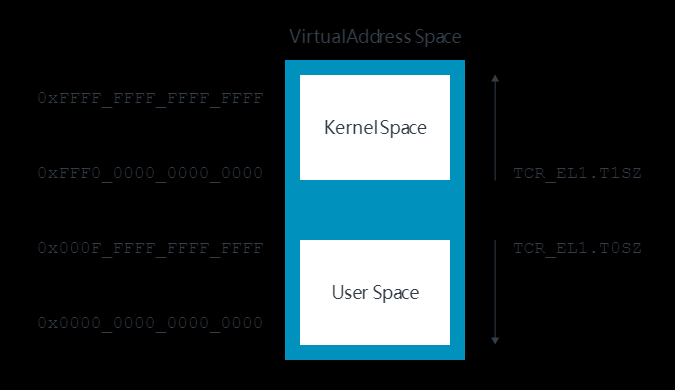

Each region of address space has a size of up to 52-bits. However, each region can be independently shrunk to a smaller size. The TnSZ fields in the TCR_ELx registers control the size of the virtual address space. For example, this diagram shows that TCR_EL1 controls the EL0/EL1 virtual address space:

地址空间的每个区域的大小最多为 52 位。然而,每个区域都可以独立地缩小到更小的尺寸。 TCR_ELx 寄存器中的 TnSZ 字段控制虚拟地址空间的大小。例如,下图显示 TCR_EL1 控制 EL0/EL1 虚拟地址空间:

Address Space Identifiers - Tagging translations with the owning process

地址空间标识符 - 使用所属进程标记翻译

Virtual Machine Identifiers - Tagging translations with the owning VM

虚拟机标识符 - 使用所属虚拟机标记翻译

The Memory Management Unit (MMU) 内存管理单元

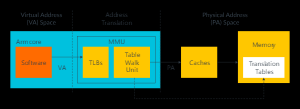

The Memory Management Unit (MMU) is responsible for the translation of virtual addresses used by software to physical addresses used in the memory system.

内存管理单元 (MMU) 负责将软件使用的虚拟地址转换为内存系统中使用的物理地址。

The MMU contains the following:

MMU 包含以下内容:

The table walk unit, which contains logic that reads the translation tables from memory.

表遍历单元,包含从内存中读取转换表的逻辑。

Translation Lookaside Buffers (TLBs), which cache recently used translations.

翻译后备缓冲区 (TLB),缓存最近使用的翻译。

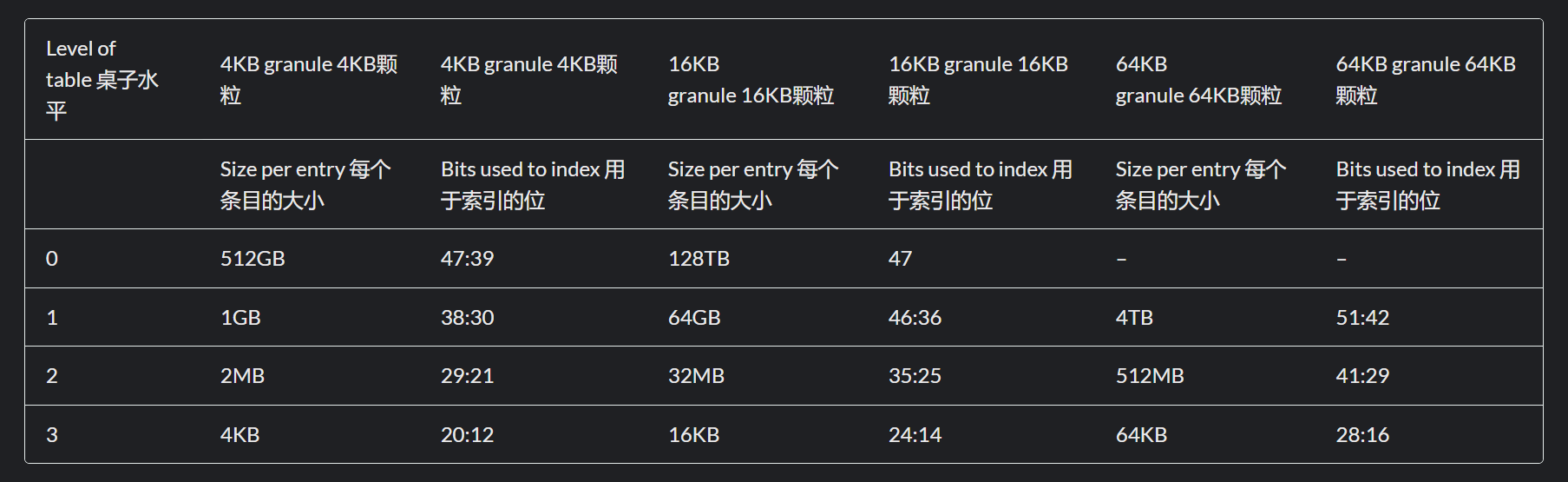

Translation granule 翻译颗粒

Translation Lookaside Buffer maintenance 翻译后备缓冲区维护

The TLBI instruction is used to invalidate entries in the TLBs. The syntax of this instruction is:

TLBI 指令用于使 TLB 中的条目无效。该指令的语法为:TLBI < type >< level >{IS|OS} {, < xt >}

STR X1, [X5] // Write to translation table entry

DSB ISH // Barrier instructions - not covered in this guide

TLBI VAAE1IS , X0 // Invalidate VA specified by X0, in EL0/1

// virtual address space for all ASIDs

DSB ISH // Barrier instructions - not covered in this guide

ISB // Synchronize context on this processor

这段代码是一个在 ARM 架构中用于更新和管理翻译表项的过程:

STR X1, [X5]:将寄存器 X1 的值存储到由 X5 指定的内存地址,即更新翻译表项。

DSB ISH:数据同步屏障,确保之前的所有内存操作都完成后再继续。

TLBI VAAE1IS, X0:无效化由 X0 指定的虚拟地址在 EL0/EL1 虚拟地址空间中的翻译缓存(TLB),适用于所有 ASID。

再次执行 DSB ISH 和 ISB,确保所有之前的指令已执行完毕并且上下文已同步。

这个流程确保了翻译表项的更新在所有处理器上都同步生效。